# A Delay-Adjustable, Self-Testable Flip-Flop for Soft-Error Tolerability and Delay-Fault Testability

Dave Y.-W. Lin, ChungLi Tang, and Charles H.-P. Wen *ECE Dept., NCTU, Taiwan*

### Outline

- Introduction

- Enhancing Testability for Soft-Error Tolerance by DAST-FF

- Preliminary

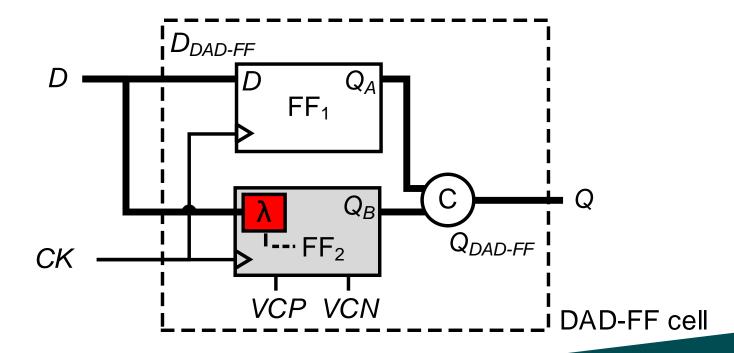

- DAD-FF: Soft-Error Tolerable Flip-Flop

- Method

- Experimental Results

- Conclusion

# Introduction

# Introduction (1/3)

- In the general soft-error tolerable circuit design, its capability of soft-error tolerability (SET) is untestable and unverifiable, resulting in an unreliable system.

- From the perspective of design for testability (DUT), the untestable

SET is not acceptable.

# Introduction (2/3)

- As a result, we extend our previous radiation-hardened design:

Delay-Adjustable D-Flip-Flop (DAD-FF) as Delay-Adjustable and

Self-Testable Flip-Flop (DAST-FF).

- Both DAD-FF and DAST-FF are hardened by delay latching (detailed in Preliminary).

# Introduction (3/3)

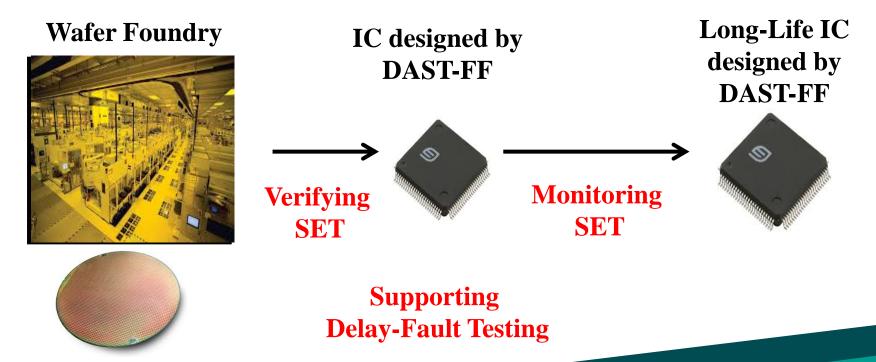

• To sum up, our proposed DAST-FF can (1) verify SET after manufactured, and (2) monitor SET during IC's life time.

# 2. Preliminary

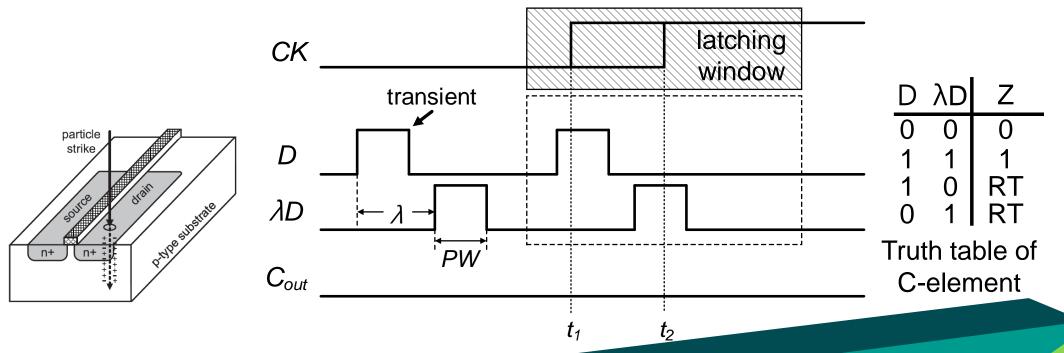

# Delay-Latching Technique (1/3)

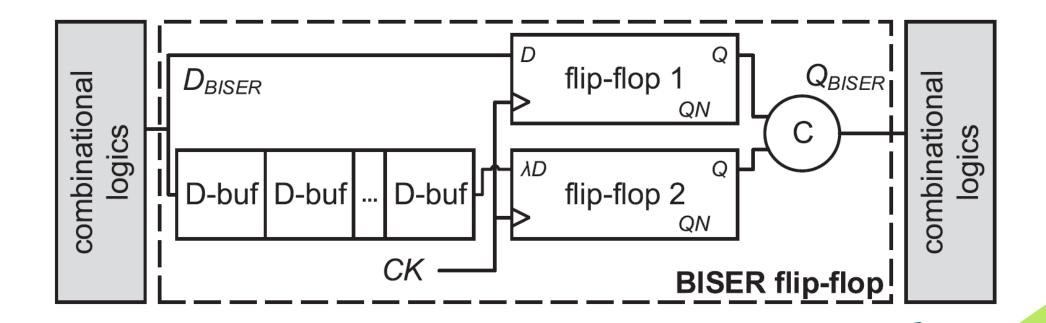

The basis of DAST-FF: DAD-FF and BISER, which utilize the latching delay for detecting soft errors.

# Delay-Latching Technique (2/3)

- Dual-module redundancy

- Typical data path

- Delayed data path

# Delay-Latching Technique (3/3)

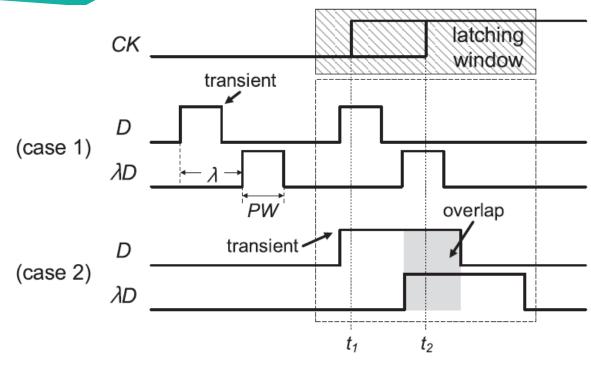

Case 1: latching delay  $\lambda > PW$

Case 2: latching delay  $\lambda$  < PW

Transient in gray area are undetectable, indicating that λ has significant impact on SET.

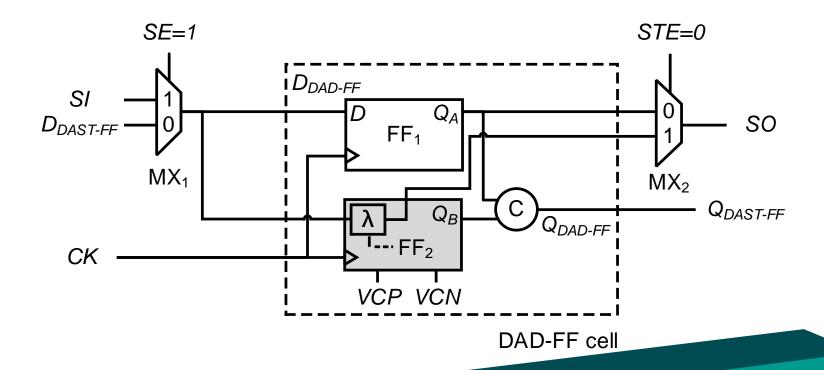

## Recap DAD-FF and \( \lambda \)

- Dual data path (original and delayed data path)

- λ is the key factor to detect soft errors.

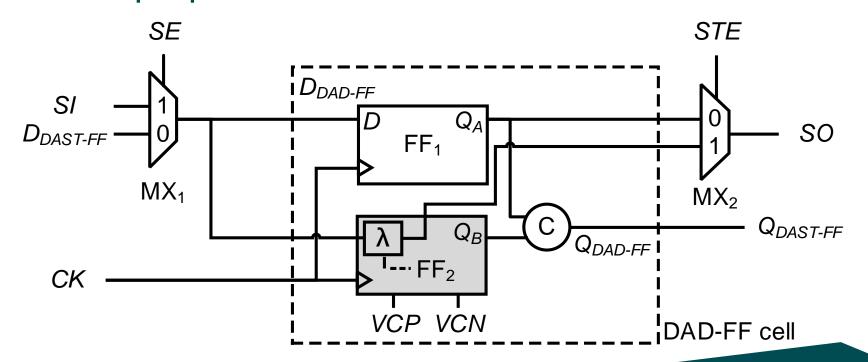

# 3. DAST-FF: Delay-Adjustable and Self-Testable Flip-Flop

# DAST-FF (1/2)

- The major purpose of DAST-FF is to make λ testable.

- The second purpose of DAST-FF is scannable.

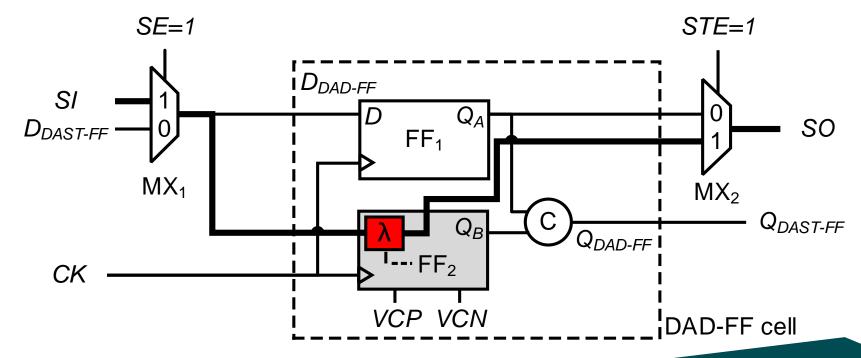

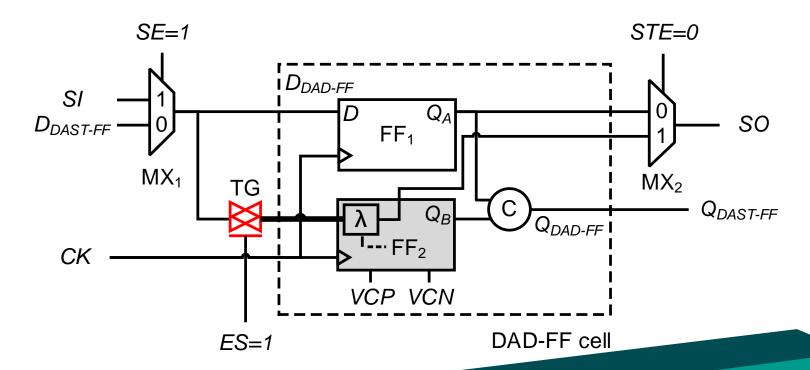

# **DAST-FF (2/2)**

- SE (scan enable) = 1, STE (self-test enable) = 1

- In NanGate45,  $Delay_{SI-SO} = 278ps (\lambda = 166ps)$

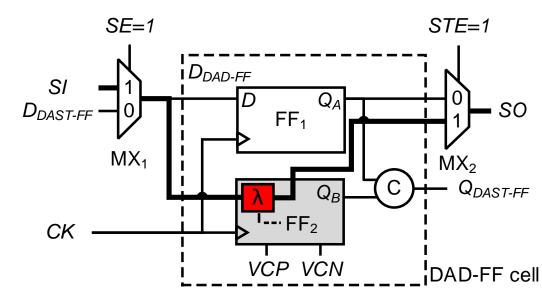

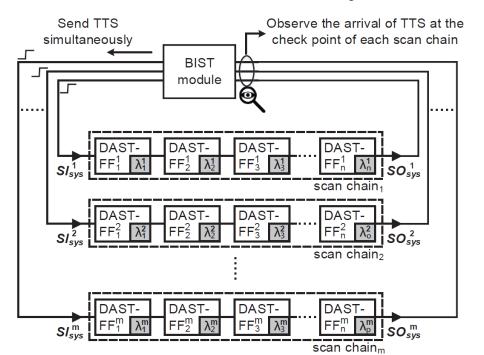

## Built-In Self-Test for λ

- Accumulating λs for better testability

- Single  $\lambda$  is too tiny

- Increase the overall BIST time

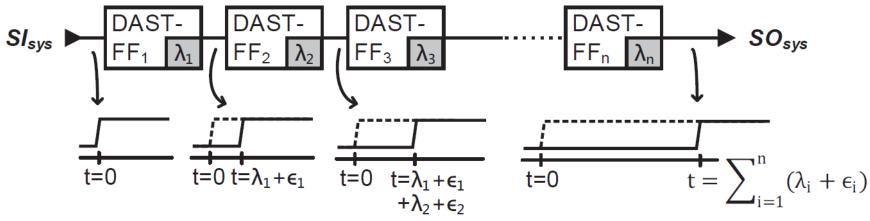

## Concurrent BIST for \(\lambda\)

#### For multiple scan-chain design

#### Advantage:

- Concurrent λ self test

- Minimize test time

- No additional routing or placing requirement

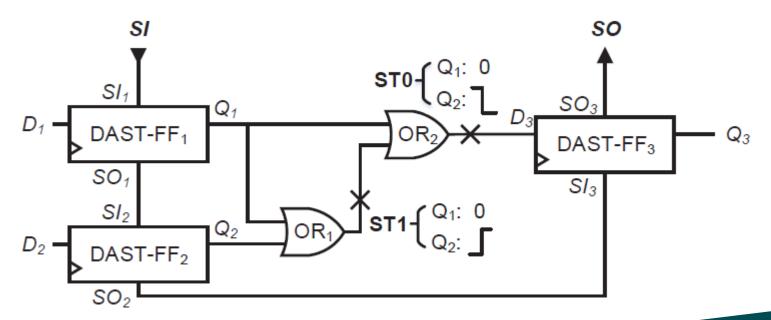

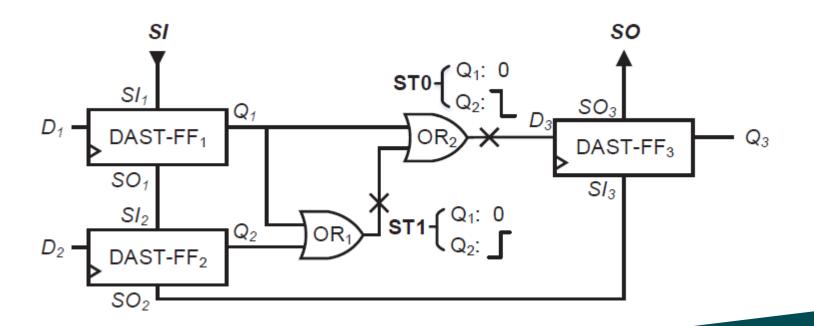

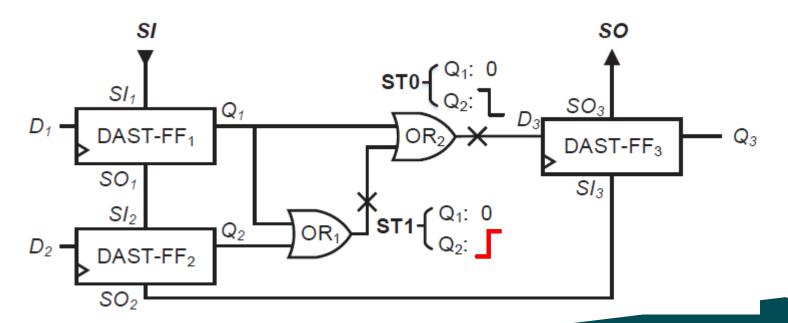

# Delay-Fault Testing (1/2)

- DAST-FF increases testability on delay faults

- ST0: slow-to-0 fault

- ST1: slow-to-1 fault

# Delay-Fault Testing (2/2)

Traditional Launch on Capture (LOC) and Launch on Shift (LOS) cannot detect such ST1.

# Enhanced Delay-Fault Testing (1/4)

- Enhanced scan-delay test:

- Generate arbitrary transition in each FF

- Method: add additional latch to store complementary values

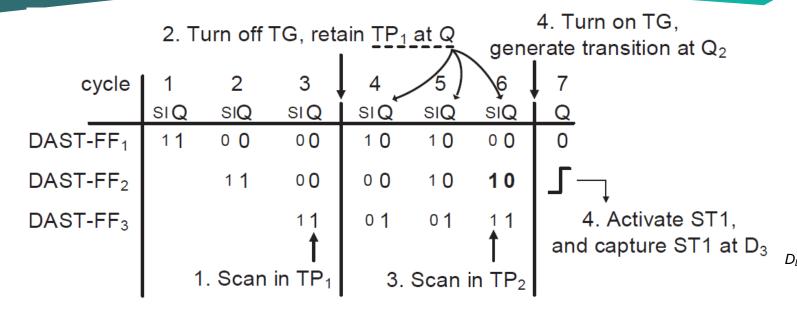

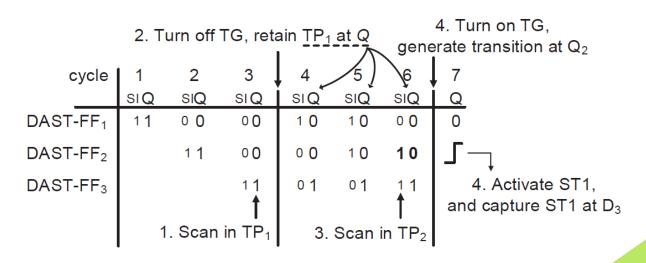

# Enhanced Delay-Fault Testing (2/4)

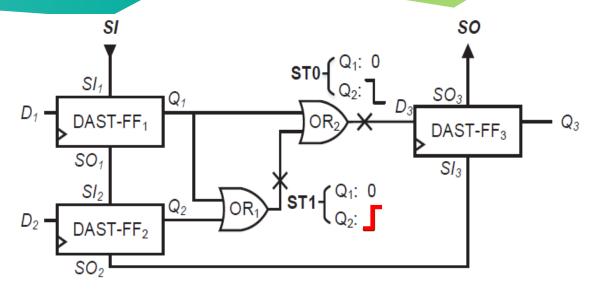

Our DAST-FF has dual storage nodes originally.

# Enhanced Delay-Fault Testing (3/4)

- Our DAST-FF has dual storage nodes originally.

- Transmission gate (TG) is added to store complementary values

# Enhanced Delay-Fault Testing (4/4)

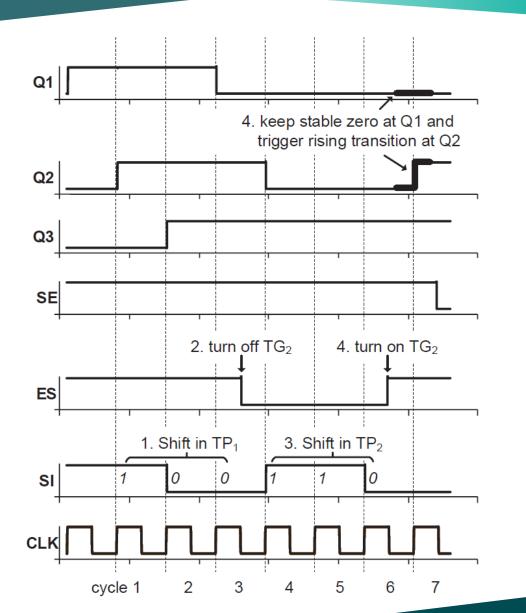

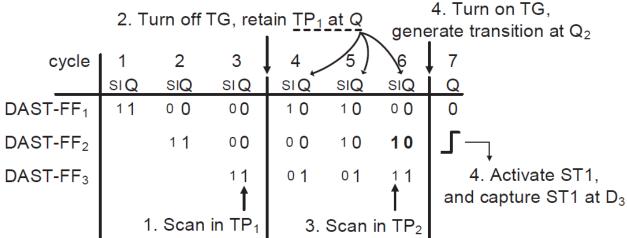

$SI_{0} = \begin{bmatrix} SI_{1} & ST_{0} & SI_{1} & SI_{2} & SI_{3} &$

VCP VCN

ES=1

DAD-FF cell

CK

- Scan in TP₁=001

- 2. Turn off TG and retain TP₁ at FF₁

- 3. Scan in  $TP_2=011$

- 4. Turn on TG and generate a rising transition

# 4. Experimental Results

## **Experimental Results**

- Experimental results can be divided into 2 parts:

- λ-based BIST

- Enhanced delay-fault testing

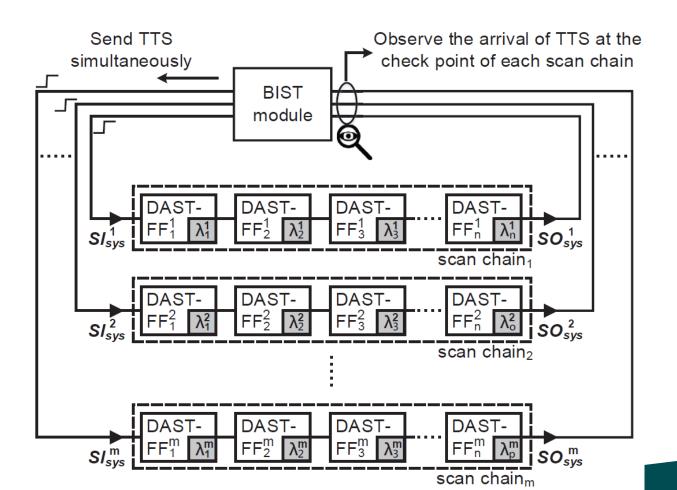

# **λ-Based Concurrent BIST**

TABLE I

UTILIZING SELF-TEST MODE TO ESTIMATE ACCUMULATED DELAYS OF THE SCAN CHAIN BY DAST-FF

FOR SOFT-ERROR-TOLERABILITY VERIFICATION

|                                           | DMA by       | DAST-FF      | des_perf by DAST-FF |              |              |              |              |              |  |

|-------------------------------------------|--------------|--------------|---------------------|--------------|--------------|--------------|--------------|--------------|--|

| # of DAST-FF/                             | 2192/        |              | 8802/               |              |              |              |              |              |  |

| total gates                               | 25301        |              | 111229              |              |              |              |              |              |  |

| # of scan chain                           | SC           | = 1          | SC = 3              |              |              |              |              |              |  |

| # of DAST-FF                              | N = 2192     |              | $N_1 = 3405$        |              | $N_2 = 3217$ |              | $N_3 = 2180$ |              |  |

| in scan chain                             |              |              |                     |              |              |              |              |              |  |

| Intrinsic delay                           | 0.112        |              | 0.112               |              | 0.112        |              | 0.112        |              |  |

| $\epsilon$ (ns)                           |              |              |                     |              |              |              |              |              |  |

| latching delay                            | 0.145        | 0.166        | 0.145               | 0.166        | 0.145        | 0.166        | 0.145        | 0.166        |  |

| $\lambda$ (ns)                            | 0.145        | 0.100        | 0.140               | 0.100        | 0.140        | 0.100        | 0.145        | 0.100        |  |

| Target energy level                       | 20           | 32           | 20                  | 32           | 20           | 32           | 20           | 32           |  |

| LET (MeV-cm <sup>2</sup> /mg)             | $(>3\sigma)$ | $(>6\sigma)$ | $(>3\sigma)$        | $(>6\sigma)$ | $(>3\sigma)$ | $(>6\sigma)$ | $(>3\sigma)$ | $(>6\sigma)$ |  |

| Overall delay $(\Lambda)$ of scan chain   |              |              |                     |              |              |              |              |              |  |

| $\Lambda = N \times (\lambda + \epsilon)$ | 563.3        | 609.4        | 875.1               | 946.6        | 826.8        | 894.3        | 560.3        | 606.0        |  |

| (ns)                                      |              |              |                     |              |              |              |              |              |  |

| Check point (CP) in BIST                  |              |              |                     |              |              |              |              |              |  |

| $CP = \Lambda/T_{clk}$                    | 563          | 609          | 875                 | 946          | 826          | 894          | 560          | 606          |  |

| (cycle)                                   | iom : :      | · /Tl 1      |                     |              |              |              |              |              |  |

<sup>\*</sup>Given the clock period in the BIST circuit is  $T_{clk} = 1$  ns.

# **Enhanced Delay-Fault Testing**

# Comparison

TABLE II

COMPARING PROPOSED DAST-FF WITH GENERIC DAD-FF, SCAN DAD-FF,

SEU-TOLERANT ENHANCED SCAN FLIP-FLOP, AND GENERIC ENHANCED SCAN FLIP-FLOP

|               | Soft-error<br>tolerability |           | Testability           |               |          | Required resource    |                      |  |

|---------------|----------------------------|-----------|-----------------------|---------------|----------|----------------------|----------------------|--|

|               | SET                        | SEU       | Scannable             | Enhance       | Self     | Number of additional | Number of additional |  |

|               | tolerable                  | tolerable |                       | scan testable | testable | controlling signals  | scan in/out          |  |

| SFF [9]       |                            | ./        |                       |               | 1        | 2                    |                      |  |

|               |                            |           | ·                     |               |          | (SE)                 | (SI, SO)             |  |

| DTES-FF [6]   | /                          | ((stable) |                       | 2             | 2        |                      |                      |  |

|               |                            |           | <b>~</b>              | √(stable)     |          | (SE, HS)             | (SI, SO)             |  |

| ECEE CED [10] |                            | (         | /                     | ((stable)     |          | 2                    | 2                    |  |

| ESFF-SED [10] |                            | <b>√</b>  | $\checkmark$ (stable) |               |          | (SE, HS)             | (SI, SO)             |  |

| UTES-FF [7]   |                            |           | ✓ ✓                   | √(unstable)   |          | 2                    | 4                    |  |

| U1E3-FF [7]   |                            | <b>√</b>  | <b>'</b>              |               |          | (SE, CNF)            | (SIP, SIN, SOP, SON) |  |

| DAST-FF       | <b>√</b>                   | ✓         | ✓                     | √(stable)     | ✓        | 3                    | 2                    |  |

|               |                            |           |                       |               |          | (SE, SD, ES)         | (SI, SO)             |  |

# 5. Conclusion

# Conclusion (1/2)

- DAST-FF can not only tolerate soft-errors but also verify its softerror tolerability by BIST.

- BIST module takes only 946ns for a design with 8802 FF to verify

> 6σ soft-error protection.

- DAST-FF also supports enhanced delay-fault testing, incurring only 4.5% area overhead.

# Conclusion (2/2)

To sum up, our proposed DAST-FF can (1) verify SET after manufactured, and (2) monitor SET during IC's life time.